# EEL 3712L LOGIC DESIGN I LAB

### Practice for Final – Summer, 2019

## Instructor: Abdullah Aydeger

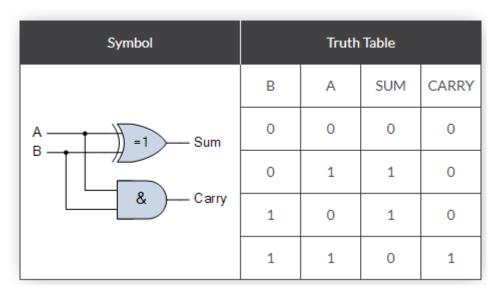

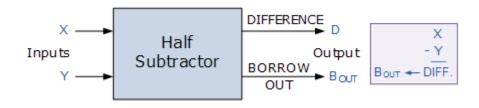

1. Design a *half* adder/subtract Circuit with XOR, AND and Inverter (whichever needed) gates.

#### Answer:

$SUM = A XOR B = A \oplus B$

$$CARRY = A AND B = A.B$$

Half Subtractor with Borrow-out

$$D = X \text{ XOR } Y = X \bigoplus Y \qquad \qquad B = \text{not-X AND } Y$$

| Symbol      |   | Ті | ruth Table |        |

|-------------|---|----|------------|--------|

|             | Y | х  | DIFFERENCE | BORROW |

| X = 1 Diff. | 0 | 0  | 0          | 0      |

|             | 0 | 1  | 1          | 0      |

| Borrow      | 1 | 0  | 1          | 1      |

|             | 1 | 1  | 0          | 0      |

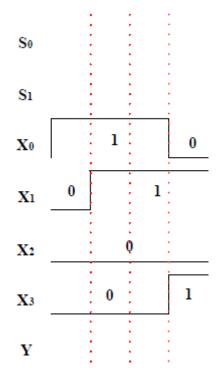

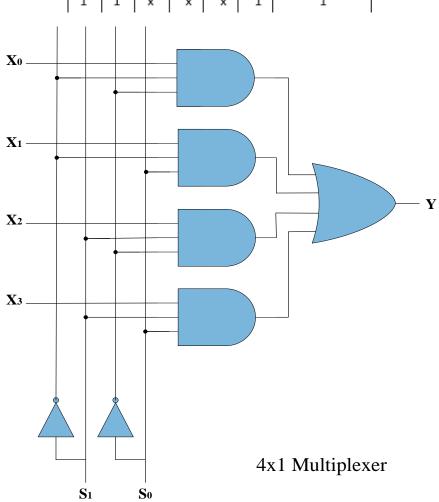

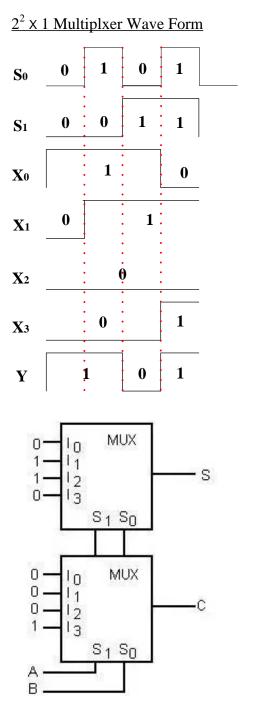

- 2. Design a 4-to-1 Multiplexer with gates and invertors.

- a. Make the Truth table and the equation, you may use De Morgan' Law convert into universal gates(NAND and NOR) for the diagram

- b. Draw the diagram

- c. Complete the waveform

- d. Design Half-adder using this MUX(es).

$\underline{\textbf{Answer:}} Y = S'_1 \cdot S'_0 \cdot X_0 + S'_1 \cdot S_0 \cdot X_1 + S_1 \cdot S'_0 \cdot X_2 + S_1 \cdot S_0 \cdot X_3$

|    |    | Inp | outs |    |    | Output |

|----|----|-----|------|----|----|--------|

| So | S1 | X₀  | Xı   | X2 | Х₃ | Y      |

| 0  | 0  | 0   | x    | х  | х  | 0      |

| 0  | 0  | 1   | х    | х  | х  | 1      |

| 1  | 0  | х   | 0    | х  | х  | 0      |

| 1  | 0  | х   | 1    | х  | х  | 1      |

| 0  | 1  | х   | х    | 0  | х  | 0      |

| 0  | 1  | х   | х    | 1  | х  | 1      |

| 1  | 1  | х   | х    | х  | 0  | 0      |

| 1  | 1  | х   | х    | х  | 1  | 1      |

#### 4 X 1 Multiplexer Truth Table

S = sum

C =carry-out

A and B are inputs (A+B)

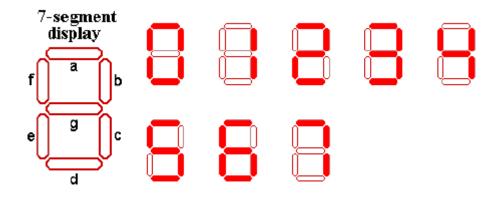

3. 7-Segment Octal Number (from 0 to 7) display driver could display the octal number given by the three inputs I2I1I0 using a 7-Segment LED device as shown in Fig 1. The truth table for this circuit is in Tab. 4, please fill in it and write the Minterms of each segment of LED display for this driver.

Binary-coded Octal to 7-Segment Display Decoder Truth Table

| Dec | coder In | put | Decoder<br>Outputs | Inputs of Common Cathode<br>7-Segment LED Display |   |   |   |   |   |   |

|-----|----------|-----|--------------------|---------------------------------------------------|---|---|---|---|---|---|

| I2  | Iı       | I0  | (Octal#)           | а                                                 | b | с | d | е | f | g |

|     |          |     |                    |                                                   |   |   |   |   |   |   |

|     |          |     |                    |                                                   |   |   |   |   |   |   |

|     |          |     |                    |                                                   |   |   |   |   |   |   |

|     |          |     |                    |                                                   |   |   |   |   |   |   |

|     |          |     |                    |                                                   |   |   |   |   |   |   |

|     |          |     |                    |                                                   |   |   |   |   |   |   |

Write Minterms of:

$$a=\Sigma (0, 2, 3, 5, 6, 7)$$

b= e=

c= f=

d= g=

#### Answer:

Binary-coded Octal to 7-Segment Display Decoder Truth Table

| Der | oder In                        | +11t    | Decoder   | Inputs of Common Cathode |                             |   |   |   |         |   |  |

|-----|--------------------------------|---------|-----------|--------------------------|-----------------------------|---|---|---|---------|---|--|

| Det | Jouer III                      | ւթու    | Outputs   |                          | 7-Segment LED Display       |   |   |   |         |   |  |

| I2  | Iı                             | Io      | (Octal#)  | a                        | b                           | с | d | е | f       | g |  |

| 0   | 0                              | 0       | 0         | 1                        | 1                           | 1 | 1 | 1 | 1       | 0 |  |

| 0   | 0                              | 1       | 1         | 0                        | 1                           | 1 | 0 | 0 | 0       | 0 |  |

| 0   | 1                              | 0       | 2         | 1                        | 1                           | 0 | 1 | 1 | 0       | 1 |  |

| 0   | 1                              | 1       | 3         | 1                        | 1                           | 1 | 1 | 0 | 0       | 1 |  |

| 1   | 0                              | 0       | 4         | 0                        | 1                           | 1 | 0 | 0 | 1       | 1 |  |

| 1   | 0                              | 1       | 5         | 1                        | 0                           | 1 | 1 | 0 | 1       | 1 |  |

| 1   | 1                              | 0       | 6         | 1                        | 0                           | 1 | 1 | 1 | 1       | 1 |  |

| 1   | 1                              | 1       | 7         | 1                        | 1                           | 1 | 0 | 0 | 0       | 0 |  |

| а   | l=∑ ((                         | ), 2, 3 | , 5, 6, 7 | $e = \sum (0, 2, 6)$     |                             |   |   |   |         |   |  |

| b   | $b=\sum (0, 1, 2, 3, 4, 7)$    |         |           |                          | 7) $f=\sum (0, 4, 5, 6)$    |   |   |   |         |   |  |

| с   | $c=\sum (0, 1, 3, 4, 5, 6, 3)$ |         |           |                          | 7) $g=\sum (2, 3, 4, 5, 6)$ |   |   |   | 4, 5, 6 | ) |  |

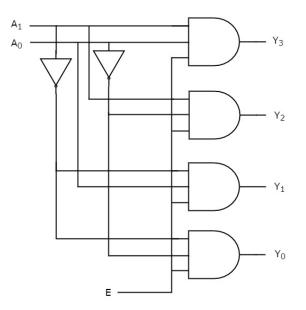

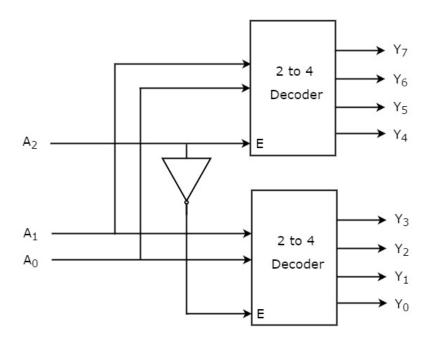

4. Design **Active-High** Output 2 to 4 Binary Decoder using AND gates. Consider Enable input for your design. Show the truth table. By using this decoder, design 3 to 8 decoder.

#### Answer:

$d=\sum (0, 2, 3, 5, 6)$

| Enable | Inp        | outs           | Outputs        |                |            |                |  |

|--------|------------|----------------|----------------|----------------|------------|----------------|--|

| E      | <b>A</b> 1 | A <sub>0</sub> | Y <sub>3</sub> | Y <sub>2</sub> | <b>Y</b> 1 | Y <sub>0</sub> |  |

| 0      | х          | х              | 0              | 0              | 0          | 0              |  |

| 1      | 0          | 0              | 0              | 0              | 0          | 1              |  |

| 1      | 0          | 1              | 0              | 0              | 1          | 0              |  |

| 1      | 1          | 0              | 0              | 1              | 0          | 0              |  |

| 1      | 1          | 1              | 1              | 0              | 0          | 0              |  |

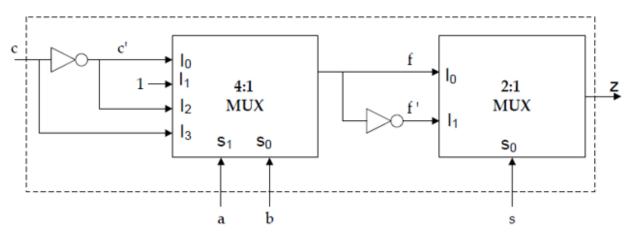

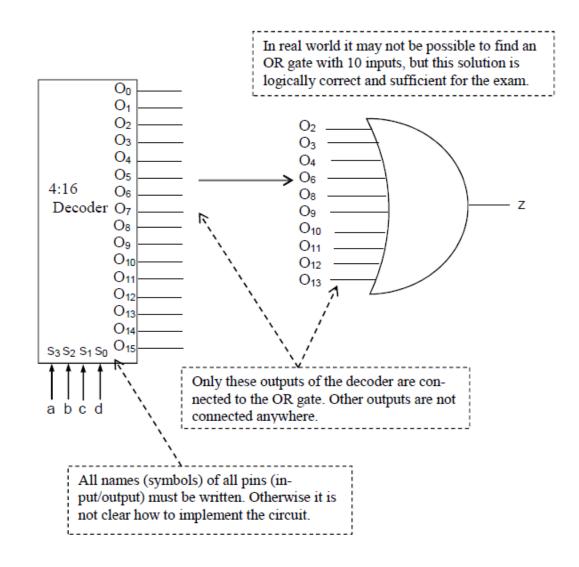

- 5. (a) Construct truth table of the schematic.

- (b) Write the expression (equation) of Z = f(a,b,c,d).

(c) Design and draw same function using 4:16 decoder.

#### Answer:

| Truth table:           |                                                                        |

|------------------------|------------------------------------------------------------------------|

| a b c d z<br>0 0 0 0 0 |                                                                        |

| 00010                  |                                                                        |

| 00101                  |                                                                        |

| 00111                  |                                                                        |

| 01001                  |                                                                        |

| 01010                  |                                                                        |

| 01101                  |                                                                        |

| 01110                  |                                                                        |

| 10001                  |                                                                        |

| 10011                  |                                                                        |

| 10101                  |                                                                        |

| 10111                  |                                                                        |

| 11001                  |                                                                        |

| 11011                  |                                                                        |

| 11100                  | z= a'b'cd'+ a'b'cd + a'bc'd'+ a'bcd'+ ab'c'd'+ ab'c'd + ab'cd' + ab'cd |

| 1111 0                 | + abc'd'+ abc'd                                                        |

**<u>Remember that</u>** a'b'c'd' + a'b'c'd = a'b'c'(d' + d) = a'b'c'

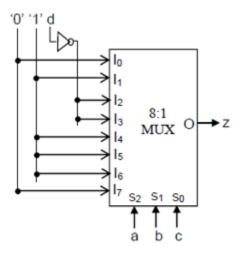

6. Write the truth table of following function and then design the schematic using MUX(es) and 2 inverter gates.

If

$$s0 = 0$$

then  $z = f(a,b,c) = a'b + bc + b'c'$

If s=1 then z = f'(a,b,c)

c.

$$s \rightarrow f/f$$

## Answer:

|     | f(S=0) | С | b | а |

|-----|--------|---|---|---|

| c'  | 1      | 0 | 0 | 0 |

| U U | 0      | 1 | 0 | 0 |

| 1   | 1      | 0 | 1 | 0 |

|     | 1      | 1 | 1 | 0 |

|     | 1      | 0 | 0 | 1 |

| c'  | 0      | 1 | 0 | 1 |

|     | 0      | 0 | 1 | 1 |

| С   | 1      | 1 | 1 | 1 |